© Universiti Tun Hussein Onn Malaysia Publisher's Office

# IJIE

Journal homepage: <a href="http://penerbit.uthm.edu.my/ojs/index.php/ijie">http://penerbit.uthm.edu.my/ojs/index.php/ijie</a>

ISSN: 2229-838X e-ISSN: 2600-7916

The International

Journal of

Integrated

Engineering

# Effects of High-k Dielectric Materials on Electrical Performance of Double Gate and Gate-All-Around MOSFET

# Nor Fareza Kosmani<sup>1</sup>, Fatimah A. Hamid<sup>2</sup>, M. Anas Razali<sup>1</sup>\*

<sup>1</sup>Faculty of Electrical and Electronic Engineering, Universiti Tun Hussein Onn Malaysia, 86400, Batu Pahat, Johor, MALAYSIA

<sup>2</sup>Faculty of Electrical Engineering, Department of Computer and Electronics Engineering, Universiti Teknologi Malaysia, 81310 UTM, Johor Bahru, Johor, MALAYSIA

DOI: https://doi.org/10.30880/ijie.2020.12.02.010 Received 29 December 2019; Accepted 27 January 2020; Available online 28 February 2020

Abstract: This paper presents the electrical behaviour of Double Gate (DG) and Gate-All-Around nanowire (GAA) MOSFET using different high permittivity (high-k) gate dielectric materials. In order to study the influence of high-k dielectric material towards DG and GAA, Atlas Silvaco TCAD tools were used to simulate the device and to determine the electrical characteristics. The high-k materials chosen in this study were Silicon Nitride (Si3N4), Aluminium Oxide (Al2O3), Zirconium Oxide (ZrO2) and Hafnium Oxide (HfO2). The gate dielectric materials have played a significant role in the design of novel and high performances at nanoscale of electrical devices. It can be observed that when approaching a higher value of dielectric constant, the on current increases while the subthreshold slope (SS) threshold voltage (Vth) and leakaga current reduced. It can be observed that HfO2 shows the best performance compared to other simulated dielectric materials for both DG and GAA MOSFET.

Keywords: High-k dielectric, Double Gate MOSFET, Gate-All-Around MOSFET

#### 1. Introduction

Recently, the miniaturization process of electronic components including transistors in integrated circuits becomes one of the main objectives in semiconductor industry. The purpose of this process is to locate more components per unit area whilst improving the performance of the device itself. Even though making the size of components smaller gives a better resolution, there will always be drawbacks arising during the CMOS scaling process. One major weakness is short channel effects (SCE) that eventually degrades the device performances. However, recently multigate transistor has been proposed to replace the planar MOSFET in order to reduce the SCE. Double Gate (DG) and Gate-All-Around (GAA) nanowire MOSFET are among the multigate transistors which potrays a good role to replace the classical MOSFET due to their ability to suppress SCE (Jena et al. 2016; Tanushree Debilata Das et al. 2017; Chowdhury et al. 2016).

Besides that, the continuous scaling of the physical dimension also leads to another problem which is high leakage current that results in high power consumption. As mention in the International Technology Roadmap for Semiconductors 2.0 (ITRS) 2015 ("International Technology Roadmap for Semiconductor 2.0" 2015), the crucial thing to be taken care of in high-performance device is the power consumption. Previous research has introduced the using of high-k dielectrics as replacement of current gate which is Silicon Dioxide,  $SiO_2$  as gate dielectric film helps to improve the leakage current and to have a better current drive. Previous study shows that high-k materials are more suitable than the  $SiO_2$  due to ability to improve leakage current while having smaller thickness of insulator (El, Hadri, and Patanè 2016).

<sup>\*</sup>Corresponding Author

Several materials have been investigated as replacement for gate dielectrics instead of SiO<sub>2</sub> such as Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>), Aluminium Oxide (Al<sub>2</sub>O<sub>3</sub>), Aluminium Nitride (AIN), Lanthanum Oxide (La<sub>2</sub>O<sub>3</sub>), Zirconium Oxide (ZrO<sub>2</sub>) and Hafnium Oxide (HfO<sub>2</sub>). These materials are chosen because they are thermodynamically stable in contact with silicon and have higher permittivity as compared to SiO<sub>2</sub> (Dueñas et al. 2012). This paper presents the study of using different high-k dielectrics and their impact towards current-voltage characteristics, on current, off current, Ion/Ioff ratio, Vth and SS.

#### 2. Device Structure and Simulation

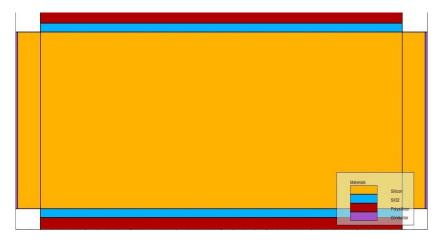

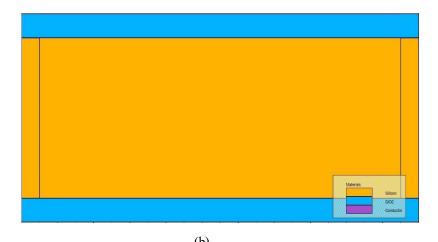

The cross-sectional views of DG and GAA nanowire are illustrated as in **Fig 1** (a) and (b). The blue colour is the oxide layer which is SiO<sub>2</sub> that will be change later to other high-k materials. The orange colour represents the channel (silicon-type), the purple layer is the conductor layer and red colour in GAA diagram is the polysilicon. The device simulations were performed using Atlas simulator in Silvaco TCAD tool. Both of DG and GAA are having the same parameter setting as shown in **Table 1**. In this study, SiO<sub>2</sub> is replaced with other different high-k dielectric materials. The high-k materials chosen in this study are Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub> and HfO<sub>2</sub>. **Table 2** shows the band offsets and dielectric constant for different dielectric materials (Chaudhary et al. 2018),(V. Kumar et al. 2011) used in this simulation.

Table 1 - Physical parameter setting for simulation structure.

| Parameter                                      | Value                       |

|------------------------------------------------|-----------------------------|

| Oxide thickness, tox                           | 1.5 nm                      |

| Silicon film thickness, tsi                    | 10 nm                       |

| $ m V_{DD}$                                    | 1V                          |

| Substrate concentration, N <sub>A</sub>        | $1x10^{15}  \text{cm}^{-3}$ |

| Drain and source concentration, $N_{\text{D}}$ | $1x10^{20}\text{cm}^{-3}$   |

| Channel length, Lg                             | 1 μm                        |

Table 2 - Properties of different high-k dielectric materials

| Material                       | Dielectric<br>Constant, к | Band gap<br>(eV) |  |  |

|--------------------------------|---------------------------|------------------|--|--|

| SiO <sub>2</sub>               | 3.9                       | 9                |  |  |

| Si <sub>3</sub> N <sub>4</sub> | 7.9                       | 5.3              |  |  |

| Al <sub>2</sub> O <sub>3</sub> | 10                        | 8.8              |  |  |

| $ZrO_2$                        | 23                        | 5.8              |  |  |

| $HfO_2$                        | 25                        | 6                |  |  |

(a)

Fig. 1 - (a) Cross-section of GAA; (b) Cross-section of DG

## 3. Results and Discussion

## 3.1 Double-gate MOSFET

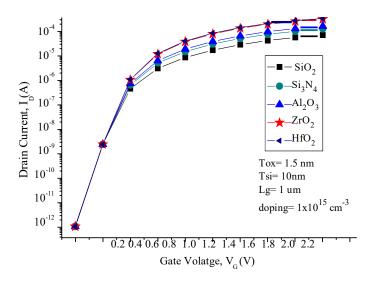

In this simulation, gate dielectric  $SiO_2$  was replaced by the chosen high-k dielectric materials which are  $S_{i3}N_4$ ,  $Al_2O_3$ ,  $ZrO_2$  and  $HfO_2$ . In order to study the effect of using high-k, the results obtained for high-k dielectric materials were then compared to the result when using  $SiO_2$  as gate dielectric. **Fig. 2** shows the Id-Vgs curve for DG when using different high-k dielectrics materials. It can be seen that  $HfO_2$  has the best transfer characteristic which is high on current followed by  $ZrO_2$ ,  $Al_2O_3$ ,  $Si_3N_4$  and  $SiO_2$  respectively. From the graph shown, it is evident that use of high-k dielectrics can improve the transfer characteristic. The results also have a good agreement with previous studies (V. Kumar et al. 2011; Chaudhary et al. 2018; Charles Pravin et al. 2016).

Fig. 2 - Id-Vgs characteristic of DG for different dielectrics constant values at VDS= 1.0V

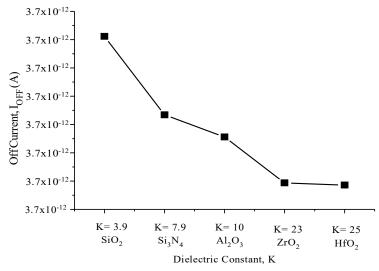

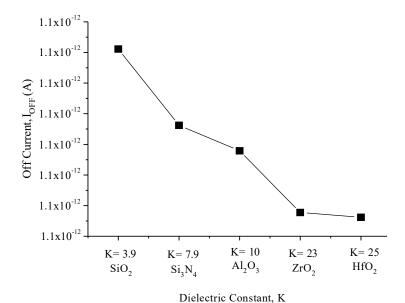

Fig. 3 represents the off current for DG MOSFET. It can be observed that the leakage current decreases exponentially when approaching higher dielectric constant value. The decrease in off-state current is basically because of the increasing of barrier potential faced by the carriers. Low off-state current leads to higher Ion/Ioff ratio. Ion/Ioff ratio is used to bench mark the devices. If the device shows higher Ion/Ioff ratio it is suitable for high-speed logic and low power applications (Magnusson 2011).

Fig. 3 - Off current for different k values for DG

#### 3.2 Gate-All-Around MOSFET

In the second part, the simulation proceeds with GAA MOSFET with the same step as DG MOSFET. Fig. 4 shows the Id-Vgs curve when different high-k dielectric materials are used. The result of high-k materials are also being compared to SiO<sub>2</sub>. For GAA, the trend of the curve is similar with DG but it has lower on current. HfO<sub>2</sub> also shows the best characteristics compared to other materials. As mention before, high-k material will directly cause the on-state current increased and the off-state current reduced due to the increase of fringing electric field. Fig. 5 shows the variation of leakage current with respect to different gate dielectric materials and exhibits an effective suppression for all the gate dielectric materials. Basically, SiO<sub>2</sub> is replaced with higher k dielectric materials to avoid direct tunnelling when the tox used is less than 2nm (Robertson and Wallace 2015). Hence, when higher k is used to replace SiO<sub>2</sub>, same capacitance but with lower tunnelling current can be achieved.

Fig. 4 - Id-Vgs characteristic of GAA for different dielectrics constant values

Fig. 5 - Off current for different k values for GAA

### 3.3 Effect of High-k Dielectric Materials in DG and GAA Towards Vth and SS

The characteristics of DG and GAA were compared to analyse which transistor is having better performance in terms of Vth and SS when high-k dielectric material is used in the simulation.

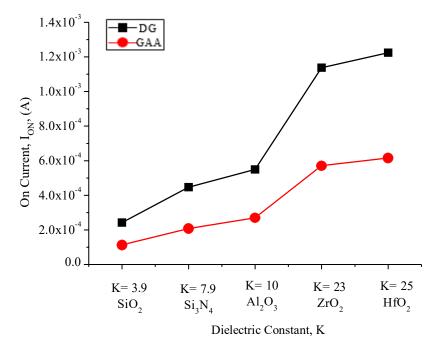

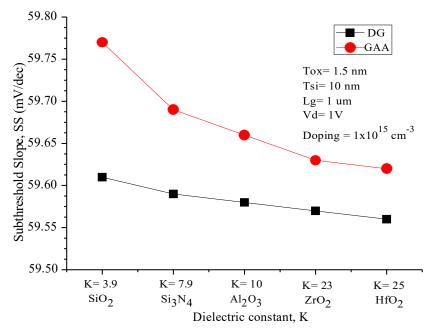

Fig. 6 shows the comparison of on state current for DG and GAA with various dielectric constant values. On state current is also one of the important parameters of a device, which determines fan out and fan in capabilities of a circuit. The on current increased when the gate oxide is replaced with higher dielectric constant material compared to SiO<sub>2</sub>. This is because the used of high-k material increase the fringing electric field in the device. Hence, the on state current will increase while reducing the off-state current (Tripathi, Mishra, and Mishra 2012). However, very large value of high-k (k>25) is not really good for suppression of short channel effects since stronger fringing fields will induce electric fields from source/drain to the channel thus results in degradation of gate control (Mohsenifar and Shahrokhabadi 2015). Result shows that DG has higher on current ratio compare to GAA. The increase in dielectric constant results in enhanced gate oxide capacitance and hence better gate control. Fig. 7 shows the SS characteristic for DG and GAA respectively. Both devices show that the SS is lower when higher dielectric constant is used. The lower the value of SS, the more efficient and rapid the switching speed of the device from the off state to the on-state current. Here it is proven that having high-k material will help to suppress SCE and hence improve the device performance. Both GAA and DG is favorable since it has nearly-ideal SS which is 60mV/dec.

Fig. 6 - The comparison of on current for DG and GAA

Fig. 7 - SS variation for different gate dielectrics for DG and GAA

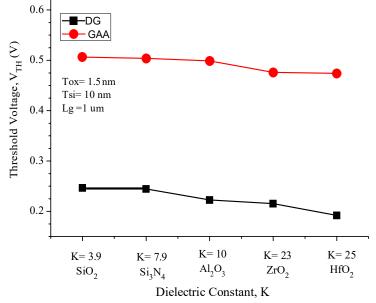

Fig. 8 shows the characteristic of Vth with the variation of high-k dielectric material for DG and GAA MOSFET respectively. Both devices exhibit similar trends which is with the increase in dielectric constant the threshold voltage of the MOSFET decreases (Dhariwal and Singh 2016) (El, Hadri, and Patanè 2016). SiO<sub>2</sub> has highest value of Vth for both DG and GAA. It is well-known that high-k materials are more suitable than the well-known SiO<sub>2</sub> due to the smaller thickness required which decreases the threshold voltage and improves the leakage characteristics of the device.

Fig. 8 - Vth with increasing dielectric constant between DG and GAA

#### 3.4 Process Variability Analysis of SiO2 and HfO2 towards Vth, SS and Leakage Current

In this section, scaling the physical dimension such as channel length, oxide thickness and channel thickness were applied in order to study their interaction towards their electrical parameter. Besides that, the simulation also focuses on the use of two different types of dielectric materials which are  $HfO_2$  and  $SiO_2$  to see the effects towards the electrical behavior.

Table 3 shows the variation of silicon film thickness towards SS and leakage current using two different types of dielectric material in DG and GAA MOSFET. It can be observed that, HfO<sub>2</sub> has lower leakage current compared to SiO<sub>2</sub> even though the silicon thickness is approaching 5 nm. It shows that HfO<sub>2</sub> has smaller SS at tsi 20 nm even compare with the SS for SiO<sub>2</sub> at 15nm for both DG nad GAA. This verifies the fact that the use of high-k is able to reduce the short

channel effects (SCEs) (Chatterjee, Chattopadhyay, and Taki 2018). For GAA, SS for higher k dielectric is better due to better gate coupling given by the high-k dielectric.

Table 4 show the effect of variation of channel length towards Vth and leakage current. Both DG and GAA exhibit the same pattern in which the Vth is increasing when approaching 100 nm channel length which in turn results in the decreasing of off-state current. At 30 nm, DG has higher leakage current when using SiO<sub>2</sub> as dielectric compared to HfO<sub>2</sub>. 30 nm is so thin that electrons can directly tunnel through the oxide, resulting in excessively high gate leakage current. However for GAA, the leakage current for HfO<sub>2</sub> is not increasing as it proves that using high-k material really helps in improving leakage current while approaching narrow channel length (R. Kumar and Mehra 2016).

Table 3 - Channel thickness vs subthreshold slope and leakage current for DG at Lg=100nm

| Channel                | DG               |                  |                  |                  | GAA              |                  |                  |                  |

|------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Thickness,<br>Tsi (nm) | SS (mV/dec)      |                  | Ioff (A)         |                  | SS (mV/dec)      |                  | Ioff (A)         |                  |

|                        | SiO <sub>2</sub> | HfO <sub>2</sub> | HfO <sub>2</sub> | SiO <sub>2</sub> | SiO <sub>2</sub> | HfO <sub>2</sub> | HfO <sub>2</sub> | SiO <sub>2</sub> |

| 5                      | 59.87            | 59.67            | 4.77E-08         | 5.52E-08         | 59.63            | 59.56            | 2.52E-13         | 2.54E-13         |

| 10                     | 60.24            | 59.85            | 1.08E-07         | 1.34E-07         | 59.78            | 59.62            | 1.08E-12         | 1.09E-12         |

| 15                     | 60.81            | 60.13            | 1.88E-07         | 2.46E-07         | 59.94            | 59.71            | 2.42E-12         | 2.45E-12         |

| 20                     | 61.72            | 60.56            | 2.98E-07         | 4.16E-07         | 60.10            | 59.82            | 4.52E-12         | 4.57E-12         |

Table 4 - Channel length vs Vth leakage current for DG and GAA

| Channel | DG               |                  |                  |          | GAA              |                  |                  |                  |

|---------|------------------|------------------|------------------|----------|------------------|------------------|------------------|------------------|

| Length  | Vth (V)          |                  | Ioff (A)         |          | Vth (V)          |                  | Ioff (A)         |                  |

| (nm)    | HfO <sub>2</sub> | SiO <sub>2</sub> | SiO <sub>2</sub> | $HfO_2$  | HfO <sub>2</sub> | SiO <sub>2</sub> | SiO <sub>2</sub> | HfO <sub>2</sub> |

| 30      | 0.20             | 0.14             | 2.59E-07         | 3.52E-09 | 0.32             | 0.34             | 3.24E-10         | 8.47E-11         |

| 60      | 0.43             | 0.39             | 2.28E-10         | 1.13E-10 | 0.41             | 0.45             | 3.31E-11         | 2.45E-11         |

| 100     | 0.44             | 0.41             | 6.39E-11         | 4.94E-11 | 0.46             | 0.49             | 1.45E-11         | 1.25E-11         |

#### 4. Conclusion

By using Atlas Silvaco TCAD tool, device design model and the simulation were performed to evaluate the electrical characteristics for DG and GAA MOSFET by using different gate dielectric material. It can be observed that towards higher value of dielectric constant, the on current and Ion/Ioff ratio, will increase while the SS, Vth and leakage current will reduce. An increased value of dielectric constant improves electrical device characteristics. Overall, HfO<sub>2</sub> shows the best performance compared to other simulated dielectric materials especially with SiO<sub>2</sub> for both DG and GAA MOSFET even in smaller dimension. GAA has better leakage current, SS characteristics when using higher k material while DG has better Vth characteristics.

#### Acknowledgement

The authors would like to acknowledge the financial support from the Research University grant of the Ministry of Higher Education (MOHE), Malaysia under the Fundamental Research Grant Scheme (FRGS) vot no 1535. Also, thanks to the Research Management Centre (RMC) of Universiti Tun Hussein Onn Malaysia (UTHM) and Universiti Teknologi Malaysia (UTM) for providing excellent research management in which to complete this work.

#### **Author's Note**

The authors declare that there is no conflict of interest regarding the publication of this article. Authors confirmed that the data and the paper is free of plagiarism.

#### References

- [1] Charles Pravin, D Nirmal, Prajoon P, Sharma Altrin, and Anuja Menokey M. (2016). Impact of gate length on the performance of a junctionless dual metal transistror with high-k dielectrics. In *Interational Conference on Devices, Circuits and Systems (ICDCS'16)*, 7-10. doi:10.1109/ICDCSyst.2016.7570594.

- [2] Chatterjee, Samprikta, Adriza Chattopadhyay, and G. S. Taki. (2018). Characteristics study of high-k gate stack for MOS-FETs using TCAD simulation. 2018 2nd International Conference on Electronics, Materials Engineering and Nano-Technology, IEMENTech 2018. IEEE, 1-6. doi:10.1109/IEMENTECH.2018.8465200.

- [3] Chaudhary, Rekha, Ravindra Mukhiya, Govind Singh, Prasantha R Mudimela, and Rishi Sharma. (2018). Simulation of MOSFET with different dielectric films. 2018 International Conference on Intelligent Circuits and Systems (ICICS). IEEE, 173-76. doi:10.1109/ICICS.2018.00044.

- [4] Chowdhury, Md. Iqbal Bahar, Muhammad Johirul Islam, Md. Jahorul Islam, Md. Mahmudul Hasan, and Sadia Ummey Farwah. (2016). Silvaco TCAD based analysis of cylindrical Gate -All-Around FET having Indium arsenide as channel and aluminium oxide as gate dielectrics. Journal of Nanotechnology and Its Applications in Engineering, 1 (1): 1-12.

- [5] Dhariwal, Sandeep, and Amandeep Singh. (2016). Analyzing the effect of gate dielectric on the leakage currents, 01028: 0-4.

- [6] Dueñas, Salvador, Helena Castán, Héctor García, and Luis Bailón. (2012). Electrical characterization of high-k dielectric gates for microelectronic devices,no. Mim.

- [7] El, Nour, Baghdad Hadri, and Salvatore Patanè. (2016). Effects of high-k dielectric materials on electrical characteristics of DG n-FinFETs. International Journal of Computer Applications, 139 (10), 28-32. doi:10.5120/ijca2016909385.

- [8] International Technology Roadmap for Semiconductor 2.0. 2015, 47.

- [9] Jena, B., B.S. Ramkrishna, S. Dash, and G.P. Mishra. (2016). Conical surrounding gate MOSFET: a possibility in gate-all-around family. Advances in Natural Sciences: Nanoscience and Nanotechnology, 7 (1). IOP Publishing. doi:10.1088/2043-6262/7/1/015009.

- [10] Kumar, Rajesh, and Rajesh Mehra. (2016). Impact analysis of DGMOSFET using high-k dielectric material. International Journal of Engineering Trends and Technology, 34 (4), 179-83. doi:10.14445/22315381/ijett-v34p237.

- [11] Kumar, Vijaya, Patrick Chella Samuel, Divya Mary Thomas, and Mohan Kumar. (2011). Analysis of dual gate MOSFETs using high k dielectrics. In 2011 3rd International Conference on Electronics Computer Technology, 1,22-25. IEEE. doi:10.1109/ICECTECH.2011.5941552.

- [12] Magnusson, Thor. (2011). Fin Field Effect Transistors performance in analog and RF for high-k dielectrics. Defence Science Journal, 61 (3), 235-40. doi:10.14429/dsj.61.695.

- [13] Mohsenifar, Saeed, and M.H. Shahrokhabadi. (2015). Gate stack high-κ materials for Si-Based MOSFETs past, present, and futures. Microelectronics and Solid-State Electronics 4 (October), 13. doi: 10.5923/j.msse.20150401.03.

- [14] Robertson, John, and Robert M. Wallace. (2015). High-K materials and metal gates for CMOS applications. Materials Science and Engineering R: Reports 88. Elsevier B.V., 1-41. doi: 10.1016/j.mser.2014.11.001.

- [15] Tanushree Debilata Das, Ramdulari Pradhan, Debabrata Singh, Adyasha Rath, and Sonali Pattnaik. (2017). Performance analysis of devices in double gate MOSFET. International Journal of Engineering and Advanced Technology (IJEAT), 7 (October), 131-36.

- [16] Tripathi, S L, Ramanuj Mishra, and R A Mishra. (2012). Multi-gate MOSFET structures with high-k dielectric materials." Journal of Electron Devices, 16, 1388-94.